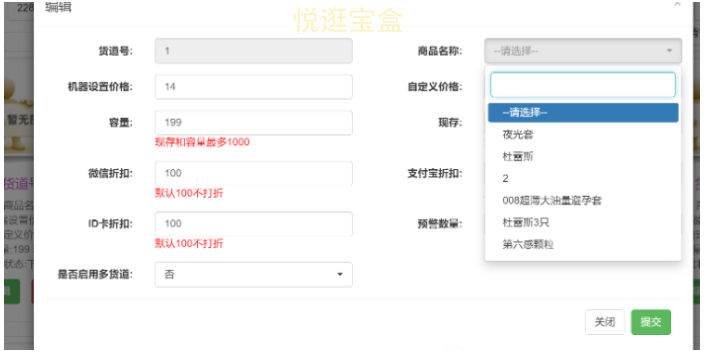

信号端口滤波需要考虑的问题点:l端口传输信号不能由于任何原因信号不完整的问题;l普通磁珠,差分滤波器会对差分信号产生衰减,深圳电气电力EMI分析整改接地,阻抗过大甚至引起差分信号时序错乱,左右信号不对称。(共模滤波器可以使差分信号顺利通过,而对共模的干扰信号呈较高阻抗);这是我从LVDS信号线上抓的一个频谱,区域的尖峰,在频谱上一直很稳定,一般这种信号是时钟串扰到信号线上的信号,必须滤除。其他在频谱上不断跳动但是频域不会变化,深圳电气电力EMI分析整改接地,深圳电气电力EMI分析整改接地,这是有用的信号,不能有所破坏。在许多国家,尤其在欧洲,对任何系统可能散发的电磁干扰有严格的限制。深圳电气电力EMI分析整改接地

有效降低电路EMI的技巧:因CMOS电路在时脉转换期间吸收的电流要高出平均流耗10mA的标准,而在时脉转换周期之间的流耗非常低甚至为零,所以辐射限制方法是电压和电流的峰值,不是平均值。在时脉转换过程中从电源至晶片电源接脚额电流浪涌是一个主要的辐射源,近端位置增加旁路电容,那晶片所需的电流直接由该电容提供,避免了电流浪涌的产生,减少了杂讯。在晶片电源接脚、I/O接口、重要讯号介面等位置增加旁路电容,有助于滤除积体电路的开关杂讯。晶片电源接脚增加旁路电容(0.1μF)处理,电容要靠近接脚摆放。深圳电气电力EMI分析整改报告由于地层的遮罩作用,使得电路对外辐射的灵敏度也会降低。

在晶片电源接脚、I/O接口、重要讯号介面等位置增加旁路电容,有助于滤除积体电路的开关杂讯。晶片电源接脚增加旁路电容(0.1μF)处理,电容要靠近接脚摆放。讯号线下方的地要完整,要有完整的参考面。讯号电流经过一个低阻抗的路径返还其驱动源,能够有效减小辐射,而且由于地层的遮罩作用,使得电路对外辐射的灵敏度也会降低。如果两个电路的参考电平不一致,就会产生功能问题,如杂讯容限和逻辑开关门限电平紊乱,这个接地杂讯电压就会导致地环路干扰的产生。

通常,高速数字电路的EMI发射带宽可以通过下面的公式计算:F=1/πTr,F为开关电路产生的高EMI频率,单位为GHz,Tr为信号的上升时间或者下降时间,单位为ns。比如,对于上升时间为1ns左右的器件,那么它所产生的高EMI频率将为350MHz,而如果上升时间降为为500ps,那么它的高EMI发射频率将为700MHz,远远高于系统正常的工作频率,这将会在一定程度上影响周围其他系统的正常工作。显然,如果能减缓信号的上升沿,将会在很大程度上减少EMI,但是随着电子设计和芯片制造水平的发展,器件总是朝着高速方向发展,单一的降低信号开关速率显然是不现实的。但我们却可以通过降低信号电压来达到同样的目的,因为在相同的时间内,低电压器件需要跨越的逻辑门电压幅度较小,就同样减缓器件的上升沿速率,所以低电压器件也是高速电路发展的趋势。EMI是如何发生的?从技朮上EMI通常由变化的电磁场及把它们导通传输。

EMI整改:1、对于差模干扰超标可调整X电容量,添加差模电感器,调差模电感量;2、对于共模干扰超标可添加共模电感,选用合理的电感量来压制;3、也可改变整流二极管特性来处理一对快速二极管如FR107一对普通整流二极管1N4007。5M以上,以共摸干扰为主,采用压制共摸的方法(整改建议)对于外壳接地的,在地线上用一个磁环串绕2-3圈会对10MHZ以上干扰有较大的衰减作用;可选择紧贴变压器的铁芯粘铜箔,铜箔闭环.处理后端输出整流管的吸收电路和初级大电路并联电容的大小。有效降低电路EMI的技巧:当存在一个磁场时,一个由导电材料形成的环路充当了天线。深圳电气电力EMI分析整改报告

晶片电源接脚增加旁路电容(0.1μF)处理,电容要靠近接脚摆放。深圳电气电力EMI分析整改接地

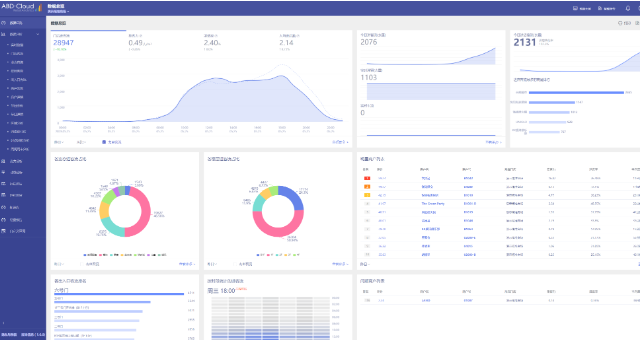

EMI,电磁干扰度,描述电子、电气产品在正常工作状态下对外界的干扰;EMI又包括传导干扰CE(conductionemission)和辐射干扰RE(radiationemission)以及谐波harmonic。EMC包括EMI(interference)和EMS(susceptibility),也就是电磁干扰和电磁抗干扰。EMC电磁能量的检测、抗电磁干扰性试验、检测结果的统计处理、电磁能量辐射压制技术、雷电和地磁等自然电磁现象、电场磁场对人体的影响、电场强度的国际标准、电磁能量的传输途径、相关标准及限制等均包含在EMC之内。EMI是电子电器产品经常遇上的问题。干扰种类有传导干扰和辐射干扰。深圳电气电力EMI分析整改接地

文章来源地址: http://smdn.chanpin818.com/ruanjian/xyzyrj/deta_11528834.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3